Technical Insights

Functionally Testing a DDR5 DIMM Is Not Difficult, but It Is Complicated!

10 min

With a rapid increase in core counts within GPU and CPU devices, there is an ever more pressing need to support more and more memory feeding these cores with data. However, in the current state of the art, memory density is not increasing at the same pace as core count, and this represents a major design challenge for server manufacturers. Simply adding memory channels to each CPU socket would result in too many memory buses and a highly cumbersome server printed circuit board architecture. This is why the industry has been working on next-generation DDR5 module architectures, and one of these architectures is the MR-DIMM module.

The MR-DIMM stands for Multiplexed-Ranked Buffered Dual In-Line Memory Module, and it is often affectionally called Mr. DIMM by the countless engineers that are working on this exciting new technology. As can be seen from the name, the MR-DIMM solution provides more memory and more bandwidth without increasing the number of memory module slots on the server board. Read on to learn about some key aspects of this design and to also learn about the test and measurement implications.

In a nutshell, the MR-DIMM architecture enables the CPU to access two ranks of memory simultaneously on a single DIMM. The benefit of this approach is that the DRAM devices themselves are not expected to operate at a faster clock frequency. However, by accessing two DRAM devices at the same time, the CPU can effectively double the memory bandwidth coming from the DIMM — brilliant!

The key to this seemingly simple solution is two-fold. First, memory controllers and registered clock drivers must be able to support the higher clock frequency. Second, the DIMM must contain an extra component on the module to allow for the multiplexing of the data between the different DRAM devices, and this is where the Multiplexed Rank Data Buffer (MDB) comes into the picture.

In previous generations of DDR memory architectures, some DIMM modules contained data buffers between the edge connector of the module and the DRAM components housed within it. However, most recent implementations of DDR5 R-DIMM modules did not require such data buffers. Now, the MR-DIMM technology changes this, and data buffers have not only come back, but they have also become central to the operating principle of the DIMM itself. Referred to as MDB, this new breed of data buffer is quite sophisticated. It enables signal conditioning at unprecedented clock frequencies, and it also has a high degree of programmability that allows it to multiplex data intelligently between memory devices.

To truly test MR-DIMM modules and the devices that make up these modules, an entirely new category of test and measurement instruments is needed. Introspect Technology has spent more than a decade honing its technology to be able to create such category of instrument. The following sections describe the three hallmarks of this category.

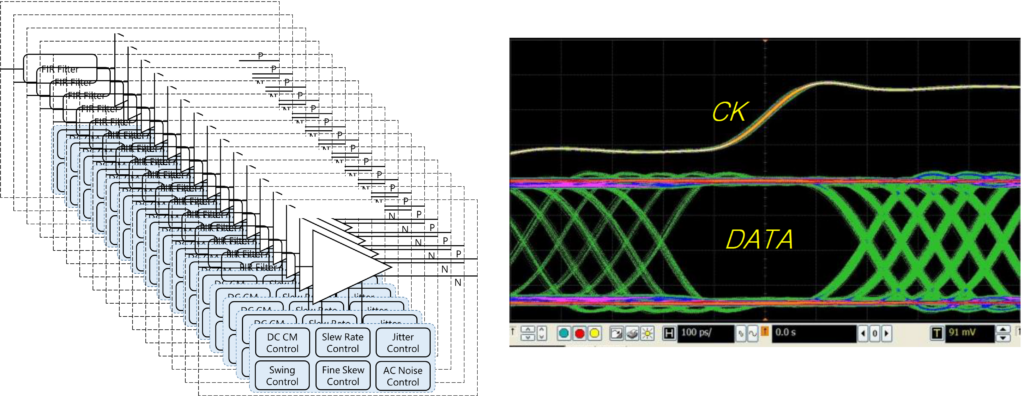

MR-DIMM technology is truly ambitious in that it creates very wide digital buses operating at speeds in excess of 17 Gbps. Testing digital receivers at these channel counts and these data rates is a tall order. What is needed is a pattern generator that can support tens of channels, each operating at a very high speed, and each having phase matching requirements that often exceed the phase matching of test cables (wires) that are used to connect them. Figure 1 illustrates this concept.

Figure 1: the need for a large number of phase-matched pattern generators.

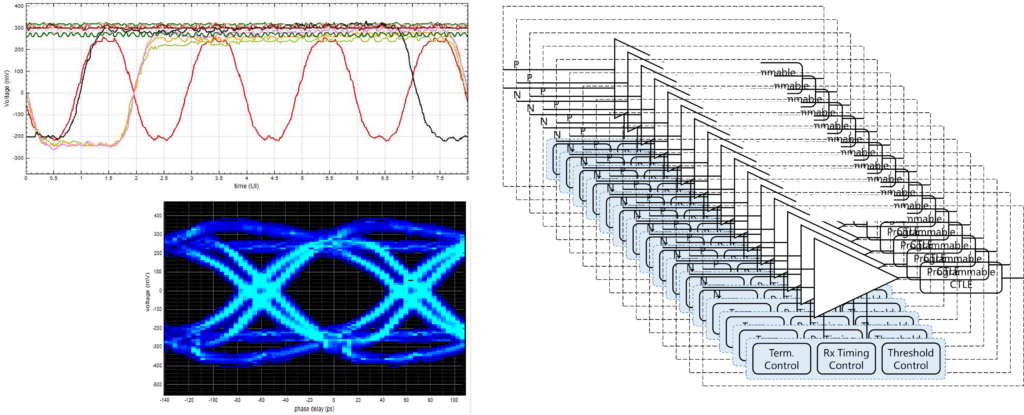

Similarly, to validate data coming from device transmitters and to characterize their analog performance, a lot of channels are needed. This is a major industry hurdle and one that Introspect Technology has tacked head-on with its test and measurement equipment. Figure 2 illustrates this concept.

Figure 2: the need for a large number of phase-matched, forwarded-clock error detectors.

Above, we have made a few mentions of the sophistication that has gone into the design of MR-DIMMs and servers containing them. This sophistication is governed by highly-detailed protocols, and these protocols must be exercised during testing.

The SV7C-17 is a category-creating ATE-on-Bench test and measurement instrument that has been created specifically for DDR5 and other memory interface technologies such as GDDR7. It is the only instrument in the world that can operate an entire DDR5 bus at data rates in excess of 17 Gbps while also being able to make parametric and training measurements on the bus. And it is powered by Pinetree, Introspect’s Python-based integrated development environment. With the SV7C-17, engineers can test and validate memory controller interfaces, component interfaces such as those found on MRCD and MDB devices, as well as entire MR-DIMM modules.

Send us an email at info@introspect.ca and ask about the SV7C-17 now!