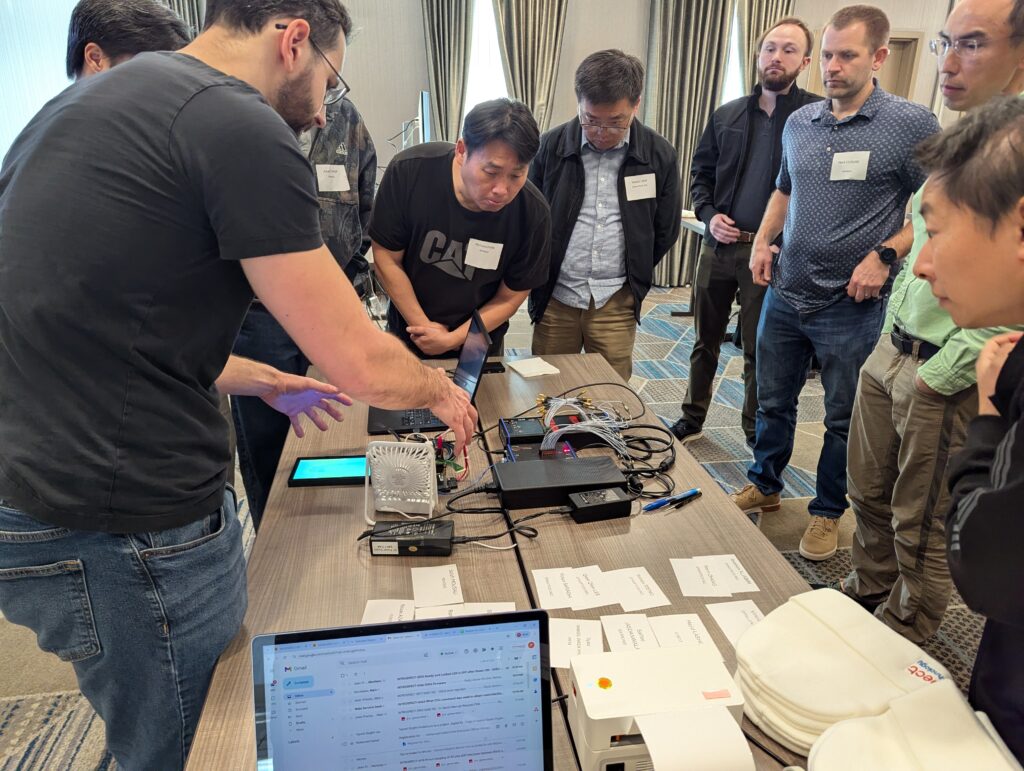

Introspect Technology hosted an in-person seminar in San Jose, California, on January 28, 2026, bringing together engineers and industry professionals working on memory interface designs.

As hardware designs continue to be driven by memory interfaces, the seminar focused on how test and measurement plays a critical role in characterizing, validating, and ultimately enabling next-generation systems.

Event Details

- Date: Wednesday, January 28, 2026

- Time: 9:30 to 15:30 PST

- Location: Fairfield by Marriott Inn & Suites San Jose North/Silicon Valley

Event Highlights

Throughout the day, attendees explored emerging standards and technologies shaping the future of memory testing, experienced live demonstrations and engaging keynotes, and connected with industry professionals over a complimentary lunch. The seminar featured:

- Real-world design validation scenarios and the advanced tools enabling them

- Live demonstrations of Introspect Technology’s DDR, LPDDR, and GDDR test solutions

- A chance to engage with memory experts and peers in the industry

- An interactive Q&A session addressing specific design challenges and use cases

Detailed Agenda

- 09:30 – 10:00 Registration, Coffee, and Pastries

- 10:00 – 10:30 Opening Address: Trends in High-Speed Memory Interface Designs

- 10:30 – 11:15 Session and Live Demo: Advanced Signal Integrity Testing Using Introspect’s Integrated-Tip Interposers with Oscilloscopes

- 11:15 – 12:00 Session and Live Demo: LPDDR5 Bus Monitoring with Introspect’s Protocol Analyzer

- 12:00 – 13:30 Complimentary Lunch

- 13:30 – 14:30 Session and Live Demo: PHY-Level Validation and Characterization on a Live DUT

- 14:30 – 15:15 Session: Introspect Technology Tools

- 15:15 – 15:30 Q&A Session