#### **C-SERIES**

SV7C

Personalized SerDes Tester

### All-in-One, Phase-Aligned Bit Error Rate Tester (BERT)

The SV7C is a parallel high-speed tester that meets the emerging test and validation requirements of increasingly complex electronic component and board designs. Operating at up to 28 Gbps and featuring 16 independent pattern generators and 16 independent signal/data analyzers, the SV7C is an all-in-one, phase-aligned bit error rate tester (BERT) and protocol exerciser and analyzer, providing self-contained functional and physical layer test and measurement capabilities for interfaces such as DisplayPort, Thunderbolt, PCI Express, and others. The SV7C integrates multiple tools into one – a pattern generator with feed-forward equalization, an error detector with programmable equalization and clock recovery, a full-functional protocol exerciser, and a full-functional protocol analyzer. It provides unprecedented insights into crosstalk and channel-to-channel variations in highly parallel systems.

#### **KEY FEATURES:**

- Data Rates: up to 28 Gbps with a fully continuous range of data rates and features 16 independent pattern generators and 16 independent signal/data analyzers.

- TX Signal Impairments: jitter injection, sinusoidal voltage noise injection, per-wire timing skew.

- Pattern Storage: 8 GBytes of High Bandwidth Memory (HBM).

- Easy to Use: Introspect's Pinetree software enables interactive operation or full automation.

#### **KEY BENEFITS:**

- Parallel: with increasing crosstalk issues, a truly parallel system allows for the most comprehensive "stress test" possible. The SV7C tests all your lanes simultaneously.

- Self-Contained: an all-in-one system reduces bench space and helps create a portable test and measurement environment; the SV7C integrates multiple tools into one.

- Automated: scripting capability is ideal for debug tasks, firmware verification, and full-fledged production screening of devices and system modules.

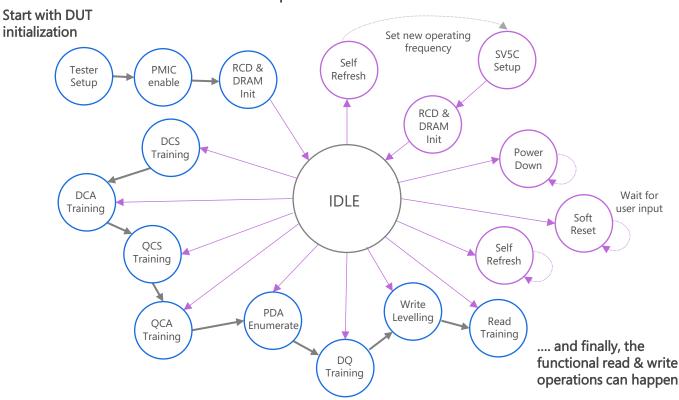

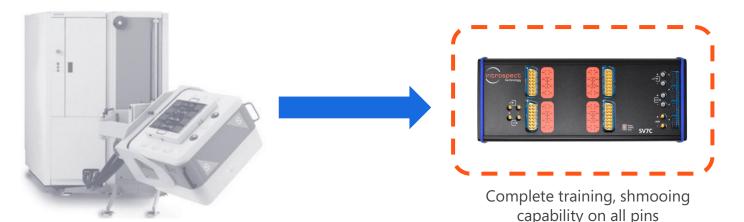

## Replace ATE for DDR Testing with the SV7C

# **General Specifications**

| PARAMETER                             | VALUE | UNITS | DESCRIPTION                                          |

|---------------------------------------|-------|-------|------------------------------------------------------|

| Number of Transmitters                | 16    |       | Capable of single-ended operation                    |

| Number of Receivers                   | 16    |       | Capable of single-ended operation                    |

| Number of Dedicated Clock<br>Outputs  | 2     |       | Individually synthesized frequency and output format |

| Number of Dedicated Clock<br>Inputs   | 1     |       | Used as external reference clock input               |

| Number of I2C/I3C<br>Controllers      | 1     |       |                                                      |

| Max Speed Entry                       | 28    | Gbps  |                                                      |

| Maximum Single-Ended<br>Voltage Swing | 400   | mV    |                                                      |

| Maximum Common Mode<br>Voltage        | 750   | mV    |                                                      |

# Simplifying Memory and Component Testing of Complicated Protocols